- RS Stock No.:

- 165-9929

- Mfr. Part No.:

- 74AUP1G07GW,125

- Manufacturer:

- Nexperia

12000 In Global stock for delivery in 4-6 working days, delivery time may vary for certain locations or FTZ

Added

Price Each (On a Reel of 3000)

MYR0.646

| Units | Per Unit | Per Reel* |

| 3000 - 3000 | MYR0.646 | MYR1,938.00 |

| 6000 - 9000 | MYR0.632 | MYR1,896.00 |

| 12000 + | MYR0.62 | MYR1,860.00 |

| *price indicative | ||

- RS Stock No.:

- 165-9929

- Mfr. Part No.:

- 74AUP1G07GW,125

- Manufacturer:

- Nexperia

Technical data sheets

Legislation and Compliance

- COO (Country of Origin):

- MY

Product Details

74AUP1G/74AUP2G/74AUP1T Family, Nexperia

For products that are Customized and under Non-cancellable & Non-returnable, Sales & Conditions apply.

74AUP Family

Industry-standard Advanced Ultra-low Power (AUP) logic family products for ultra-low power consumption, small footprint logic solutions for use in 1.8 V and mixed 1.8 V / 3.3 V circuit applications. The AUP logic family offers the following features:

Wide supply voltage range: 0.8 to 3.6V

Schmitt-trigger inputs for high noise immunity

Very low dynamic power dissipation

Enhanced ESD protection

Speed/power optimization

Schmitt-trigger inputs for high noise immunity

Very low dynamic power dissipation

Enhanced ESD protection

Speed/power optimization

Specifications

Attribute | Value |

|---|---|

| Logic Family | AUP |

| Schmitt Trigger Input | No |

| Input Type | Single Ended |

| Output Type | Open Drain |

| Mounting Type | Surface Mount |

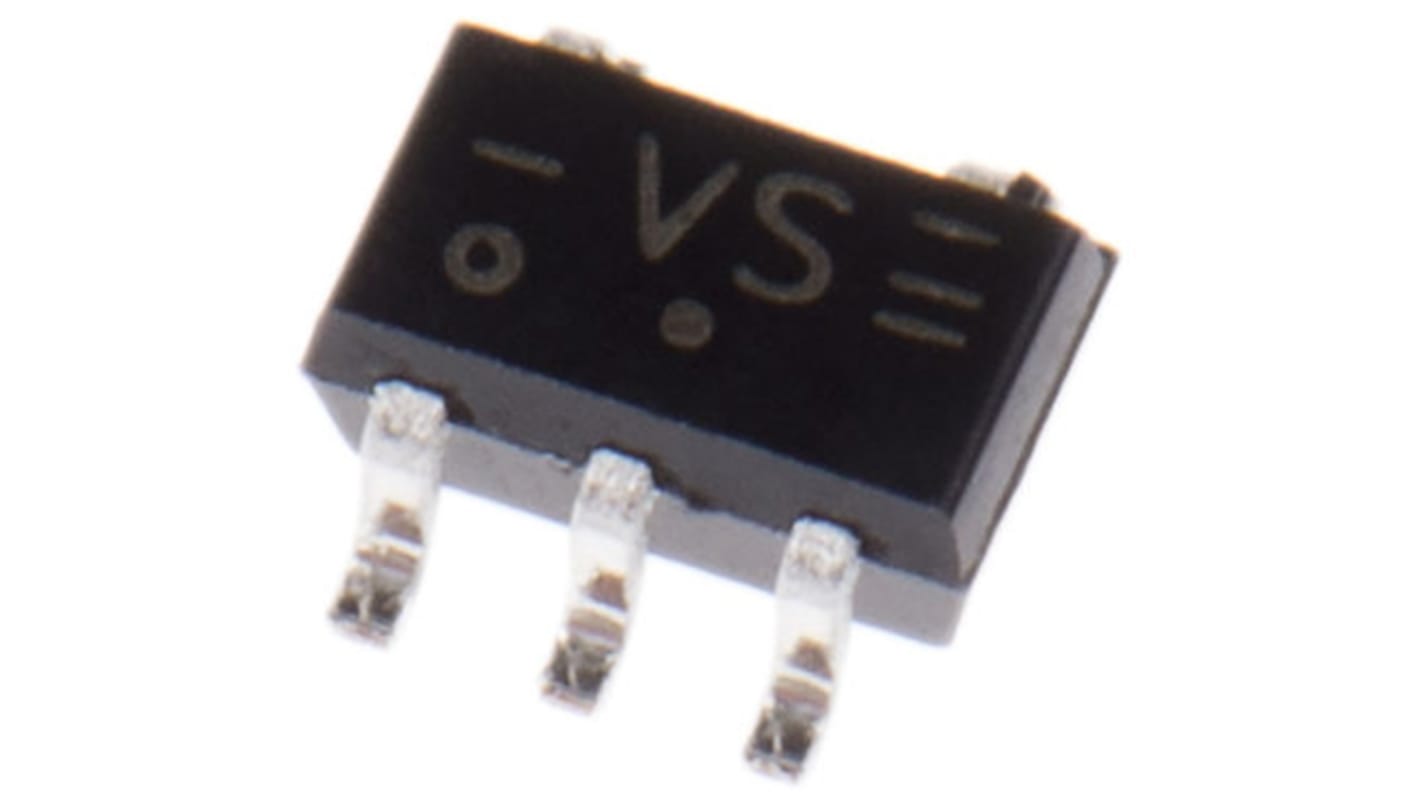

| Package Type | TSSOP |

| Pin Count | 5 |

| Maximum Low Level Output Current | 4mA |

| Maximum Propagation Delay Time @ Maximum CL | 20.7 ns @ 30 pF |

| Dimensions | 2.25 x 1.35 x 1mm |

| Maximum Operating Supply Voltage | 3.6 V |

| Maximum Operating Temperature | +125 °C |

| Height | 1mm |

| Minimum Operating Temperature | -40 °C |

| Width | 1.35mm |

| Length | 2.25mm |

| Minimum Operating Supply Voltage | 0.8 V |

| Propagation Delay Test Condition | 30pF |